1.本发明属于

芯片性能测试技术领域,具体涉及一种射频芯片筛测方法的设计。

背景技术:

2.射频芯片在制造或加工过程中,将不可避免地受到外力作用,可能产生微裂纹。同时,芯片在封装过程中也会出现包括引线变形、翘曲、芯片破裂、分层和外来颗粒等缺陷,虽然以上缺陷都有相应的缺陷检测测试方法,但是所有缺陷检测方法都不是百分百有效,导致部分存在潜在缺陷的芯片会进入芯片量产测试流程。

3.存在潜在缺陷的芯片会在后续的使用过程中,或一定的环境条件下出现性能下降、间歇性失效,甚至完全失效的风险。潜在缺陷的芯片一旦出现上述故障,将会影响电路以及整个系统的质量及可靠性,从而带来巨大的经济损失。因此提高射频芯片的出厂良品率对于提高电路以及整个系统的可靠性具有重要意义。

技术实现要素:

4.本发明的目的是为了解决现有射频芯片的缺陷检测方法无法将具有潜在缺陷的异常芯片完全筛选出来,导致部分存在潜在缺陷的射频芯片会进入芯片量产测试流程的问题,提出了一种射频芯片筛测方法。

5.本发明的技术方案为:一种射频芯片筛测方法,包括以下步骤:

6.s1、在待测射频芯片的cp测试阶段,在待测射频芯片的vdd端口依次输入五点等步进电压,并依次记录cp测试阶段每个输入电压对应的输出电流值。

7.s2、根据cp测试阶段每个输入电压对应的输出电流值计算cp测试阶段的电流一阶差值导数。

8.s3、根据cp测试阶段的电流一阶差值导数计算cp测试阶段的电流二阶差值导数。

9.s4、根据cp测试阶段的电流二阶差值导数计算cp测试阶段的电流四阶差值导数。

10.s5、针对cp测试阶段选取的n个测试标准件,重复步骤s1~s4,得到n个cp测试阶段的电流四阶差值导数,并对其求平均差,得到修正参数。

11.s6、在待测射频芯片的ft测试阶段,在待测射频芯片的vdd端口依次输入五点等步进电压,并依次记录ft测试阶段每个输入电压对应的输出电流值。

12.s7、根据ft测试阶段每个输入电压对应的输出电流值计算ft测试阶段的电流一阶差值导数。

13.s8、根据ft测试阶段的电流一阶差值导数计算ft测试阶段的电流二阶差值导数。

14.s9、根据ft测试阶段的电流二阶差值导数计算ft测试阶段的电流四阶差值导数。

15.s10、采用修正参数对ft测试阶段的电流四阶差值导数进行修正,得到修正电流四阶差值导数。

16.s11、将修正电流四阶差值导数在预设标准值范围内的待测射频芯片归入合格芯片集合bin1,将修正电流四阶差值导数不在预设标准值范围内的待测射频芯片归入失效芯

片集合bin2。

17.进一步地,步骤s1和s6中的五点等步进电压为v0-2δv,v0-δv,v0,v0+δv,v0+2δv,步骤s1中cp测试阶段每个输入电压对应的输出电流值为i

1cp

,i

2cp

,i

3cp

,i

4cp

,i

5cp

,步骤s6中ft测试阶段每个输入电压对应的输出电流值为i1,i2,i3,i4,i5,其中v0表示基准电压,δv表示电压步进值。

18.进一步地,电压v0+2δv小于或等于待测射频芯片的最大工作电压v

max

。

19.进一步地,步骤s2中cp测试阶段的电流一阶差值导数计算公式为:

20.δi

1cp

=i

2cp-i

1cp

21.δi

2cp

=i

3cp-i

2cp

22.δi

3cp

=i

4cp-i

3cp

23.δi

4cp

=i

5cp-i

4cp

24.其中δi

1cp

,δi

2cp

,δi

3cp

,δi

4cp

均为cp测试阶段的电流一阶差值导数。

25.步骤s3中cp测试阶段的电流二阶差值导数计算公式为:

26.δi

′

1cp

=δi

2cp-δi

1cp

27.δi

′

2cp

=δi

3cp-δi

2cp

28.δi

′

3cp

=δi

4cp-δi

3cp

29.其中δi

′

1cp

,δi

′

2cp

,δi

′

3cp

均为cp测试阶段的电流二阶差值导数。

30.进一步地,步骤s4中cp测试阶段的电流四阶差值导数计算公式为:

31.δi

cp

=(δi

′

2cp-δi

′

1cp

)-(δi

′

3cp-δi

′

2cp

)=-i

1cp

+5i

2cp-7i

3cp

+4i

4cp-i

5cp

32.其中δi

cp

表示cp测试阶段的电流四阶差值导数。

33.进一步地,步骤s5中修正参数的计算公式为:

[0034][0035]

其中表示修正参数,δi

dcp

为工程经验值,δi

cpi

表示第i个cp测试阶段的电流四阶差值导数。

[0036]

进一步地,步骤s7中ft测试阶段的电流一阶差值导数计算公式为:

[0037]

δi1=i

2-i1[0038]

δi2=i

3-i2[0039]

δi3=i

4-i3[0040]

δi4=i

5-i4[0041]

其中δi1,δi2,δi3,δi4均为ft测试阶段的电流一阶差值导数。

[0042]

步骤s8中ft测试阶段的电流二阶差值导数计算公式为:

[0043]

δi

′1=δi

2-δi1[0044]

δi

′2=δi

3-δi2[0045]

δi

′3=δi

4-δi3[0046]

其中δi

′1,δi

′2,δi

′3均为ft测试阶段的电流二阶差值导数。

[0047]

进一步地,步骤s9中ft测试阶段的电流四阶差值导数计算公式为:

[0048]

δi

dft

=(δi

′

2-δi

′1)-(δi

′

3-δi

′2)=-i1+5i

2-7i3+4i

4-i5[0049]

其中δi

dft

表示ft测试阶段的电流四阶差值导数。

[0050]

进一步地,步骤s10中修正电流四阶差值导数的计算公式为:

[0051][0052]

其中为修正电流四阶差值导数,表示修正参数。

[0053]

进一步地,步骤s11中预设标准值范围为其中i

low

表示预设的卡控门限最小值,i

high

表示预设的卡控门限最大值。

[0054]

步骤s11中合格芯片集合bin1为无潜在缺陷风险的芯片集合,失效芯片集合bin2为有潜在缺陷的芯片集合。

[0055]

本发明的有益效果是:

[0056]

(1)本发明可以显著遏制射频芯片量产测试的正常波动对于量产测试的干扰作用,有效拦截具有潜在缺陷的异常芯片,避免其成为合格品,从而提高射频芯片的良品率。

[0057]

(2)本发明采用基于五点等步进高阶内差比较法的iv测试方法对射频芯片进行筛测,测试速度快,测试环境简单。

[0058]

(3)本发明通过对δi

dft

进行修正后,可以有效规避因晶圆批次波动等原因造成的误杀,从而使得本发明在保证筛选的有效性的同时具有很强的批次波动适应性。

附图说明

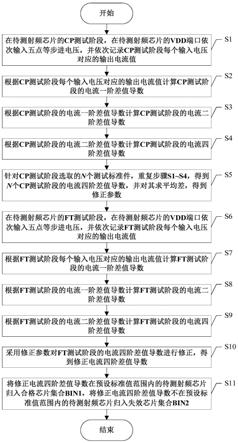

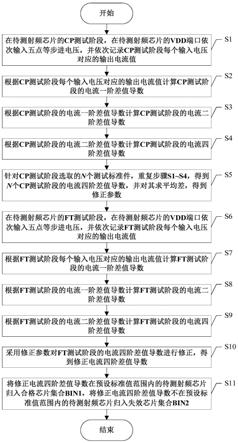

[0059]

图1所示为本发明实施例提供的一种射频芯片筛测方法流程图。

[0060]

图2所示为本发明实施例提供的待测芯片端口示意图。

[0061]

图3所示为本发明实施例提供的五点等步进电压示意图。

[0062]

图4所示为本发明实施例提供的性能正常和具有潜在缺陷的芯片电流示意图。

具体实施方式

[0063]

现在将参考附图来详细描述本发明的示例性实施方式。应当理解,附图中示出和描述的实施方式仅仅是示例性的,意在阐释本发明的原理和精神,而并非限制本发明的范围。

[0064]

本发明实施例提供了一种射频芯片筛测方法,如图1所示,包括以下步骤s1~s11:

[0065]

s1、在待测射频芯片的cp测试阶段,在待测射频芯片的vdd端口依次输入五点等步进电压,并依次记录cp测试阶段每个输入电压对应的输出电流值。

[0066]

本发明实施例中,在待测射频芯片的vdd端口输入的五点等步进电压为v0-2δv,v0-δv,v0,v0+δv,v0+2δv,对应记录得到的cp测试阶段每个输入电压对应的输出电流值为i

1cp

,i

2cp

,i

3cp

,i

4cp

,i

5cp

。

[0067]

如图2和图3所示,即在待测射频芯片的vdd端口输入电压v0-2δv,对应记录得到输出电流值i

1cp

;在待测射频芯片的vdd端口输入电压v0-δv,对应记录得到输出电流值i

2cp

;在待测射频芯片的vdd端口输入电压v0,对应记录得到输出电流值i

3cp

;在待测射频芯片的vdd端口输入电压v0+δv,对应记录得到输出电流值i

4cp

;在待测射频芯片的vdd端口输入电压v0+2δv,对应记录得到输出电流值i

5cp

。

[0092]

δi2=i

3-i2[0093]

δi3=i

4-i3[0094]

δi4=i

5-i4[0095]

其中δi1,δi2,δi3,δi4均为ft测试阶段的电流一阶差值导数。

[0096]

s8、根据ft测试阶段的电流一阶差值导数计算ft测试阶段的电流二阶差值导数,计算公式为:

[0097]

δi

′1=δi

2-δi1[0098]

δi

′2=δi

3-δi2[0099]

δi

′3=δi

4-δi3[0100]

其中δi

′1,δi

′2,δi

′3均为ft测试阶段的电流二阶差值导数。

[0101]

s9、根据ft测试阶段的电流二阶差值导数计算ft测试阶段的电流四阶差值导数,计算公式为:

[0102]

δi

dft

=(δi

′

2-δi

′1)-(δi

′

3-δi

′2)=-i1+5i

2-7i3+4i

4-i5[0103]

其中δi

dft

表示ft测试阶段的电流四阶差值导数。

[0104]

s10、采用修正参数对ft测试阶段的电流四阶差值导数进行修正,得到修正电流四阶差值导数,计算公式为:

[0105][0106]

其中为修正电流四阶差值导数,表示修正参数。

[0107]

s11、将修正电流四阶差值导数在预设标准值范围内的待测射频芯片归入合格芯片集合bin1,将修正电流四阶差值导数不在预设标准值范围内的待测射频芯片归入失效芯片集合bin2。

[0108]

本发明实施例中,预设标准值范围为其中i

low

表示预设的卡控门限最小值,i

high

表示预设的卡控门限最大值。

[0109]

本发明实施例中,合格芯片集合bin1为无潜在缺陷风险的芯片集合,失效芯片集合bin2为有潜在缺陷的芯片集合。

[0110]

如图4所示,本发明实施例中,i

low

=10,i

high

=20,则针对超出预设标准值范围的两个对应的待测射频芯片,说明其是具有潜在缺陷的,将其归入失效芯片集合bin2,其余在预设标准值范围内的待测射频芯片则归入合格芯片集合bin1。

[0111]

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。技术特征:

1.一种射频芯片筛测方法,其特征在于,包括以下步骤:s1、在待测射频芯片的cp测试阶段,在待测射频芯片的vdd端口依次输入五点等步进电压,并依次记录cp测试阶段每个输入电压对应的输出电流值;s2、根据cp测试阶段每个输入电压对应的输出电流值计算cp测试阶段的电流一阶差值导数;s3、根据cp测试阶段的电流一阶差值导数计算cp测试阶段的电流二阶差值导数;s4、根据cp测试阶段的电流二阶差值导数计算cp测试阶段的电流四阶差值导数;s5、针对cp测试阶段选取的n个测试标准件,重复步骤s1~s4,得到n个cp测试阶段的电流四阶差值导数,并对其求平均差,得到修正参数;s6、在待测射频芯片的ft测试阶段,在待测射频芯片的vdd端口依次输入五点等步进电压,并依次记录ft测试阶段每个输入电压对应的输出电流值;s7、根据ft测试阶段每个输入电压对应的输出电流值计算ft测试阶段的电流一阶差值导数;s8、根据ft测试阶段的电流一阶差值导数计算ft测试阶段的电流二阶差值导数;s9、根据ft测试阶段的电流二阶差值导数计算ft测试阶段的电流四阶差值导数;s10、采用修正参数对ft测试阶段的电流四阶差值导数进行修正,得到修正电流四阶差值导数;s11、将修正电流四阶差值导数在预设标准值范围内的待测射频芯片归入合格芯片集合bin1,将修正电流四阶差值导数不在预设标准值范围内的待测射频芯片归入失效芯片集合bin2。2.根据权利要求1所述的射频芯片筛测方法,其特征在于,所述步骤s1和s6中的五点等步进电压为v0-2δv,v0-δv,v0,v0+δv,v0+2δv,所述步骤s1中cp测试阶段每个输入电压对应的输出电流值为i

1cp

,i

2cp

,i

3cp

,i

4cp

,i

5cp

,所述步骤s6中ft测试阶段每个输入电压对应的输出电流值为i1,i2,i3,i4,i5,其中v0表示基准电压,δv表示电压步进值。3.根据权利要求2所述的射频芯片筛测方法,其特征在于,所述电压v0+2δv小于或等于待测射频芯片的最大工作电压v

max

。4.根据权利要求2所述的射频芯片筛测方法,其特征在于,所述步骤s2中cp测试阶段的电流一阶差值导数计算公式为:δi

1cp

=i

2cp-i

1cp

δi

2cp

=i

3cp-i

2cp

δi

3cp

=i

4cp-i

3cp

δi

4cp

=i

5cp-i

4cp

其中δi

1cp

,δi

2cp

,δi

3cp

,δi

4cp

均为cp测试阶段的电流一阶差值导数;所述步骤s3中cp测试阶段的电流二阶差值导数计算公式为:δi

′

1cp

=δi

2cp-δi

1cp

δi

′

2cp

=δi

3cp-δi

2cp

δi

′

3cp

=δi

4cp-δi

3cp

其中δi

′

1cp

,δi

′

2cp

,δi

′

3cp

均为cp测试阶段的电流二阶差值导数。5.根据权利要求4所述的射频芯片筛测方法,其特征在于,所述步骤s4中cp测试阶段的

电流四阶差值导数计算公式为:δi

cp

=(δi

′

2cp-δi

′

1cp

)-(δi

′

3cp-δi

′

2cp

)=-i

1cp

+5i

2cp-7i

3cp

+4i

4cp-i

5cp

其中δi

cp

表示cp测试阶段的电流四阶差值导数。6.根据权利要求1所述的射频芯片筛测方法,其特征在于,所述步骤s5中修正参数的计算公式为:其中表示修正参数,δi

dcp

为工程经验值,δi

cpi

表示第i个cp测试阶段的电流四阶差值导数。7.根据权利要求2所述的射频芯片筛测方法,其特征在于,所述步骤s7中ft测试阶段的电流一阶差值导数计算公式为:δi1=i

2-i1δi2=i

3-i2δi3=i

4-i3δi4=i

5-i4其中δi1,δi2,δi3,δi4均为ft测试阶段的电流一阶差值导数;所述步骤s8中ft测试阶段的电流二阶差值导数计算公式为:δi

′1=δi

2-δi1δi

′2=δi

3-δi2δi

′3=δi

4-δi3其中δi

′1,δi

′2,δi

′3均为ft测试阶段的电流二阶差值导数。8.根据权利要求7所述的射频芯片筛测方法,其特征在于,所述步骤s9中ft测试阶段的电流四阶差值导数计算公式为:δi

dft

=(δi

′

2-δi

′1)-(δi

′

3-δi

′2)=-i1+5i

2-7i3+4i

4-i5其中δi

dft

表示ft测试阶段的电流四阶差值导数。9.根据权利要求8所述的射频芯片筛测方法,其特征在于,所述步骤s10中修正电流四阶差值导数的计算公式为:其中为修正电流四阶差值导数,表示修正参数。10.根据权利要求9所述的射频芯片筛测方法,其特征在于,所述步骤s11中预设标准值范围为其中i

low

表示预设的卡控门限最小值,i

high

表示预设的卡控门限最大值;所述步骤s11中合格芯片集合bin1为无潜在缺陷风险的芯片集合,失效芯片集合bin2为有潜在缺陷的芯片集合。

技术总结

本发明公开了一种射频芯片筛测方法,该方法能够筛选出具有潜在缺陷的异常芯片,解决了现有射频芯片的缺陷检测方法不能将具有潜在缺陷的异常芯片完全筛选出来的技术问题。本发明可以显著遏制射频芯片量产测试的正常波动对于量产测试的干扰作用,有效拦截具有潜在缺陷的异常芯片,避免其成为合格品,从而提高射频芯片的良品率。本发明采用基于五点等步进高阶内差比较法的IV测试方法对射频芯片进行筛测,测试速度快,测试环境简单。测试环境简单。测试环境简单。

技术研发人员:吕继平 邬海峰 王测天 钟丹 廖学介 刘莹 李仁侠 陈长风 黄敏 童伟

受保护的技术使用者:成都嘉纳海威科技有限责任公司

技术研发日:2021.09.26

技术公布日:2022/1/18

声明:

“射频芯片筛测方法与流程” 该技术专利(论文)所有权利归属于技术(论文)所有人。仅供学习研究,如用于商业用途,请联系该技术所有人。

我是此专利(论文)的发明人(作者)

591

编辑:中冶有色技术网

来源:成都嘉纳海威科技有限责任公司

591

编辑:中冶有色技术网

来源:成都嘉纳海威科技有限责任公司

举报 0

举报 0

收藏 0

收藏 0

反对 0

反对 0

点赞 0

点赞 0